# Embedded Systems Design (630470)

Lecture 8

# **Interrupts in Microcontrollers**

**Prof. Kasim M. Al-Aubidy**

Computer Eng. Dept.

### **Interrupts:**

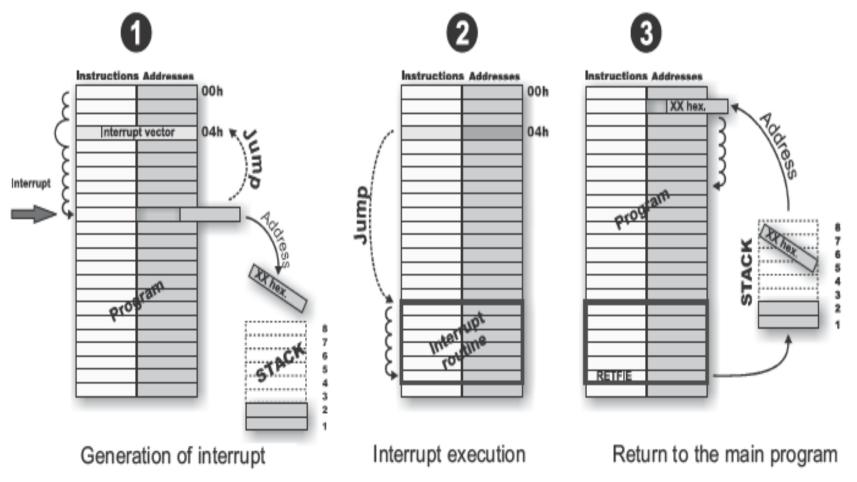

Interrupts are a mechanism which enables MC to respond to some events, regardless of what MC is doing at that time.

Each interrupt changes the program flow, interrupts it and after executing an interrupt routine, it continues from that same point on.

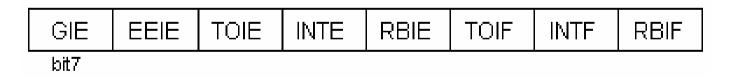

| GIE  | EEIE | TOIE | INTE | RBIE | TOIF | INTF | RBIF |

|------|------|------|------|------|------|------|------|

| bit7 |      |      |      |      |      |      |      |

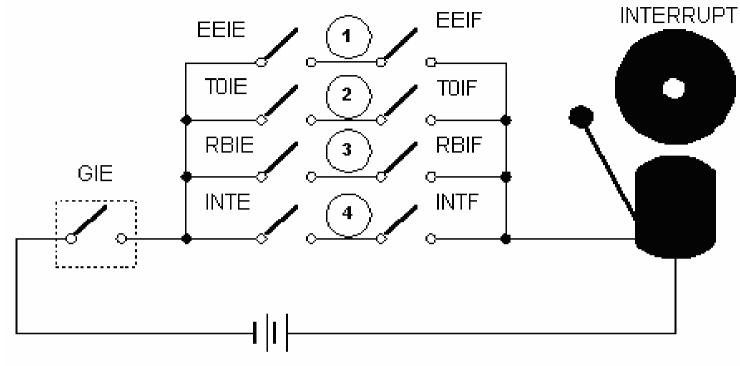

### INTCON Register:

Bit 7: GIE (Global Interrupt Enable bit): enables or disables all INTs.

*Bit 6:* **EEIE** (*EEPROM Write Complete Interrupt Enable bit*): enables an INT at the end of a writing routine to EEPROM.

If EEIE and EEIF are set simultaneously, an INT will occur.

*bit 5:* **TOIE** (*TMR0 Overflow Interrupt Enable bit*): enables INTs during TMR0 overflow.

If TOIE and TOIF are set simultaneously, interrupt will occur.

*Bit 4:* **INTE** (*INT External Interrupt Enable bit*): enables external INT from pin RB0/INT.

*Bit 3* **RBIE** (*RB port change Interrupt Enable bit*): enables INTs to occur at the change of status of pins 4, 5, 6, and 7 of port B.

If RBIE and RBIF are simultaneously set, an INT will occur.

Bit 2: **TOIF** (*TMR0 Overflow Interrupt Flag bit*): Overflow of counter TMR0.

Bit must be cleared in program in order for an INT to be detected.

Bit 1: INTF (INT External Interrupt Flag bit) External INT occurred.

If a rising or falling edge was detected on pin RB0/INT, INTF is set.

*Bit 0:* **RBIF** (*RB Port Change Interrupt Flag bit*): informs about changes on pins 4, 5, 6 and 7 of port B.

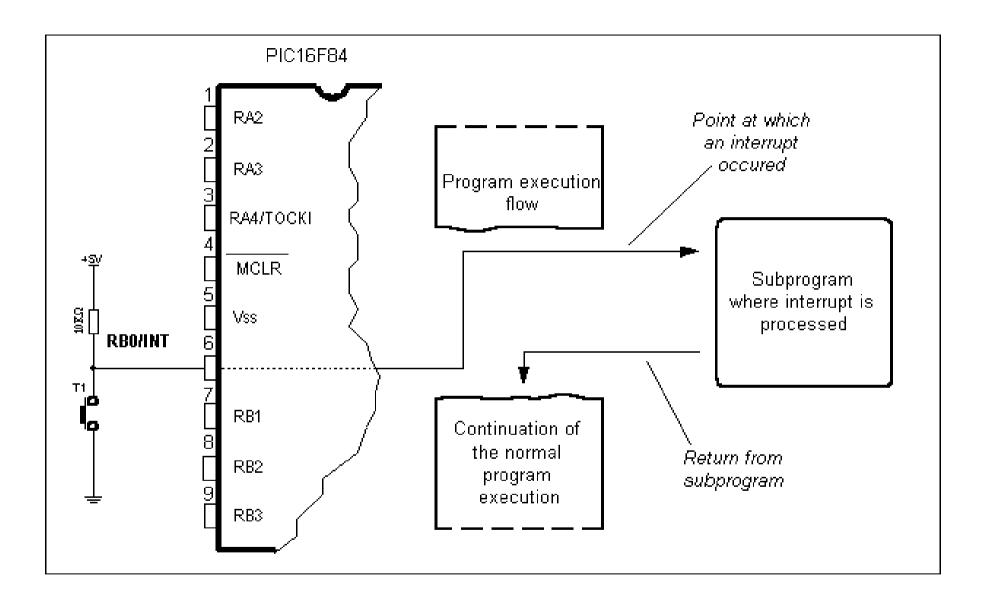

Simplified outline of PIC16F84 microcontroller interrupt

PIC16F84 has four interrupt sources:

- 1. Termination of writing data to EEPROM

- 2. TMR0 interrupt caused by timer overflow

- 3. Interrupt during alteration on RB4, RB5, RB6 and RB7 pins of port B.

- 4. External interrupt from RB0/INT pin of microcontroller.

### **External interrupt on RB0/INT pin:**

External interrupt on RB0/INT pin is triggered by rising signal edge (if bit INTEDG=1 in OPTION<6> register), or falling edge (if INTEDG=0). When correct signal appears on INT pin, INTF bit is set in INTCON register. INTF bit (INTCON<1>) must be cleared in interrupt routine, so that interrupt wouldn't occur again while going back to the main program. Interrupt can be turned off by resetting INTE control bit (INTCON<4>).

#### Interrupt during a TMR0 counter overflow:

Overflow of TMR0 counter (from FFh to 00h) will set T0IF (INTCON<2>) bit. This is very important interrupt because many real problems can be solved using this interrupt.

#### Interrupt upon a change on pins 4, 5, 6 and 7 of port B

Change of input signal on PORTB <7:4> sets RBIF (INTCON<0>) bit.

Four pins RB7, RB6, RB5 and RB4 of port B, can trigger an interrupt which occurs when status on them changes from logic one to logic zero, or vice versa.

•For pins to be sensitive to this change, they must be defined as input. If any one of them is defined as output, interrupt will not be generated at the change of status. If they are defined as input, their current state is compared to the old value which was stored at the last reading from port B.

#### Interrupt upon finishing write-subroutine to EEPROM

This interrupt is of practical nature only. Since writing to one EEPROM location takes about 10ms (which is a long time in the notion of a MC), it doesn't pay off to a MC to wait for writing to end.

Thus interrupt mechanism is added which allows the MC to continue executing the main program, while writing in EEPROM is being done in the background.

When writing is completed, interrupt informs the MC that writing has ended. EEIF bit, through which this informing is done, is found in EECON1 register. Occurrence of an interrupt can be disabled by resetting the EEIE bit.

### **Interrupt initialization:**

Touse an interrupt mechanism of a MC, some initialization tasks need to be performed.

By initialization we define to what interrupts the MC will respond, and which ones it will ignore.

| clrf INTCON       | ; | all interrupts disabled            |

|-------------------|---|------------------------------------|

| movlw B'00010000' | ; | external interrupt only is enabled |

| bsf INTCON, GIE   | ; | occurrence of interrupts allowed   |

The above example shows initialization of external interrupt on RB0 pin of a MC. Occurrence of other interrupts is not allowed, and interrupts are disabled altogether until GIE bit is set to one.

## INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0                                             | V-0 R/W-0 R/W-0                                 |                                              | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-x |  |  |  |

|---------------------------------------------------|-------------------------------------------------|----------------------------------------------|-------|-------|-------|-------|-------|--|--|--|

| GIE                                               | GIE EEIE TOIE                                   |                                              | INTE  | RBIE  | TOIF  | INTF  | RBIF  |  |  |  |

| bit 7                                             |                                                 | 1                                            |       |       |       |       | bit O |  |  |  |

| bit 7 GIE: Global Interrupt Enable bit            |                                                 |                                              |       |       |       |       |       |  |  |  |

| bit 6                                             | ) EE                                            | EEIE: EE Write Complete Interrupt Enable bit |       |       |       |       |       |  |  |  |

| bit 5 T0IE: TMR0 Overflow Interrupt Enable bit    |                                                 |                                              |       |       |       |       |       |  |  |  |

| bit 4 INTE: RB0/INT External Interrupt Enable bit |                                                 |                                              |       |       |       |       |       |  |  |  |

| bit 3 RBIE: RB Port Change Interrupt Enable bit   |                                                 |                                              |       |       |       |       |       |  |  |  |

| bit 2 T0IF: TMR0 Overflow Interrupt Flag bit      |                                                 |                                              |       |       |       |       |       |  |  |  |

| bit 1                                             | bit 1 INTF: RB0/INT External Interrupt Flag bit |                                              |       |       |       |       |       |  |  |  |

| bit 0 RBIF: RB Port Change Interrupt Flag bit     |                                                 |                                              |       |       |       |       |       |  |  |  |