# Embedded Systems Design (630414)

## Lecture: 5-6 PIC Instruction Set

Prof. Kasim M. Al-Aubidy Computer Eng. Dept.

## Instruction Set in PIC16Cxx MC Family

- Complete set: 35 instructions.

- MC Architecture: RISC microcontroller.

- Instruction Types:

- 1. Data Processing Operations:

- Copy data between registers.

- Manipulate data in a single register.

- Arithmetic operations.

- Logic operations.

### 2. Program Sequence Control Operations:

- Unconditional Jump.

- Conditional Jump.

- Call.

- Control.

## Word list

- f any memory location in a microcontroller

- W work register

- **b** bit position in 'f' register

- d destination bit

- *label* group of eight characters which marks

- the beginning of a part of the program

- **TOS** top of stack

- [] option

- <> bit position inside register

Example:

## Data transfer

Transfer of data in a MC is done between W register and an 'f' register.

| Mnemor | ic   | Description        | Operation                    | Fleg | Cycle | Notes |

|--------|------|--------------------|------------------------------|------|-------|-------|

|        |      | Data transfer      |                              |      | -     |       |

| MOVEW  | k    | Move constant to W | $k \rightarrow W$            |      | 1     |       |

| MOVWF  | f    | Move VV to f       | $W \rightarrow f$            |      | 1     |       |

| MOVF   | f, d | Move f             | $f \rightarrow d$            | Z    | 1     | 1,2   |

| CLRW   | -    | Clear W            | 0 → W                        | Z    | 1     |       |

| CLRF   | f    | Clear f            | $0 \rightarrow f$            | Z    | 1     | 2     |

| SWAPF  | f, d | Swap nibbles in f  | f(7:4), (3:0) → f(3:0),(7:4) |      | 1     | 1,2   |

These instructions provide for:

- a constant being written in W register (MOVLW)

- data to be copied from W register onto RAM.

- data from RAM to be copied onto W register (or on the same RAM location, at which point only the status of Z flag changes).

-Instruction CLRF writes constant 0 in 'f ' register,

- Instruction CLRW writes constant 0 in register W.

- SWAPF instruction exchanges places of the 4-bit nibbles field inside a register.

# **Arithmetic and logic**

PIC like most MCs supports only subtraction and addition.

Flags C, DC and Z are set depending on a result of addition or subtraction.

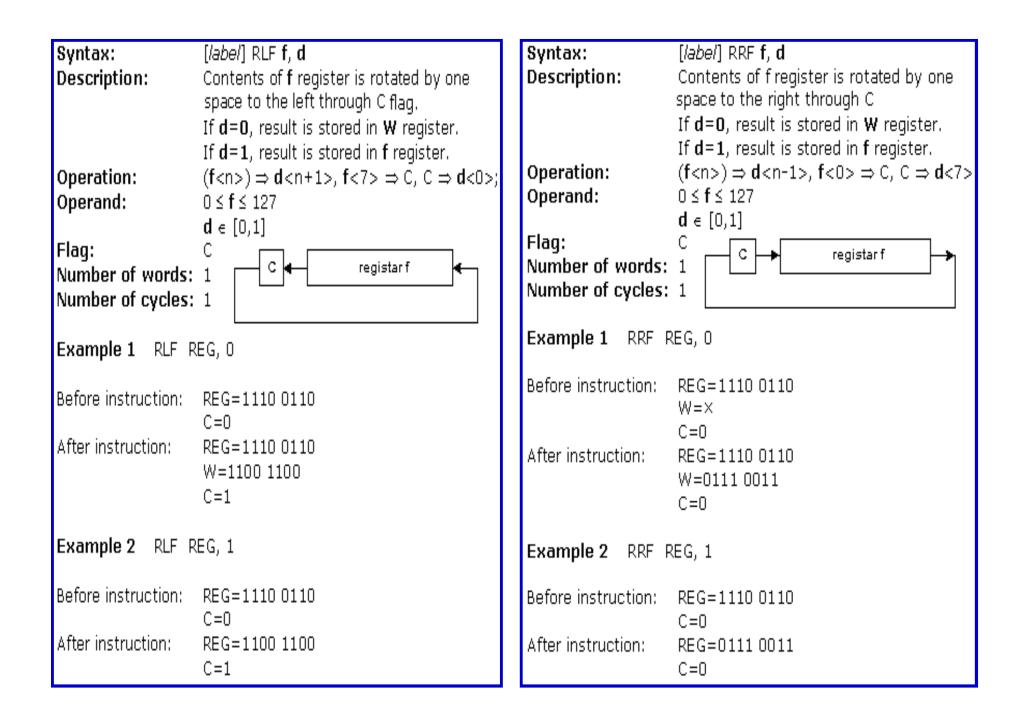

Logic unit performs AND, OR, EX-OR, complement (COMF) and rotation (RLF & RRF).

|       |      | Arritmetic and logic         |                         |        |   |     |

|-------|------|------------------------------|-------------------------|--------|---|-----|

| ADDLW | k    | Add constant and W           | $W+1 \rightarrow W$     | C,DC,Z | 1 |     |

| ADDWF | f, d | Add W and f                  | $W+f \rightarrow d$     | C,DC,Z | 1 | 1,2 |

| SUBLW | k    | Subtract W from constant     | $W-k \rightarrow W$     | C,DC,Z | 1 |     |

| SUBWF | f, d | Subtract W from f            | W-f→d                   | C,DC,Z | 1 | 1,2 |

| ANDLW | k    | AND constant with W          | $W.AND.k \rightarrow W$ | Z      | 1 |     |

| ANDWF | f, d | AND W with f                 | W.AND.f→d               | Z      | 1 | 1,2 |

| IORLW | k    | OR constant with W           | $W.OR.k \rightarrow W$  | Z      | 1 |     |

| IORWF | f, d | ORW with f                   | W.OR.f→d                | Z      | 1 | 1,2 |

| XORLW | k    | Exclusive OR constant with W | $W.XOR.k \rightarrow W$ | Z      | 1 | 1,2 |

| XORWF | f, d | Exclusive OR W with f        | W.XOR.f→d               | Z      | 1 |     |

| INCF  | f, d | Increment f                  | f+l → f                 | Z      | 1 | 1,2 |

| DECF  | f, d | Decrement f                  | $f-1 \rightarrow f$     | Z      | 1 | 1,2 |

| RLF   | f, d | Rotate Left f trough carry   |                         | С      | 1 | 1,2 |

| RRF   | f, d | Rotate Right f trough carry  |                         | С      | 1 | 1,2 |

| COMF  | f, d | Complement f                 | F→d                     | Z      | 1 | 1,2 |

### **Bit operations**

Instructions BCF and BSF do setting or cleaning of one bit anywhere in the memory. The CPU first reads the whole byte, changes one bit in it and then writes in the entire byte at the same place.

**Bit operations**

| BCF | f,b | Bit Clear f | $0 \rightarrow f(b)$ | 1 | 1,2 |

|-----|-----|-------------|----------------------|---|-----|

| BSF | f,b | Bit Set f   | $l \rightarrow f(b)$ | 1 | 1,2 |

## **Directing a program flow**

- Instructions GOTO, CALL and RETURN are executed the same way as on all other microcontrollers, only stack is independent of internal RAM and limited to eight levels.

- 'RETLW k' instruction is identical with RETURN instruction, except that before coming back from a subprogram a constant defined by instruction operand is written in W register.

| BTFSC  | f, b | Bit Test f, Skip if Clear | jump it f(b)=0                   | 1 (2) | 3     |

|--------|------|---------------------------|----------------------------------|-------|-------|

| BTFSS  | f, b | Bit Test f, Skip if Set   | jump it ք(Ն)=1                   | 1 (2) | 3     |

| DECFSZ | f, d | Decrement f, Skip if 0    | f-1 $\rightarrow$ d, jump if Z=1 | 1(2)  | 1,2,3 |

| INCFSZ | f, d | Increment f, Skip if 0    | f+l → d, jump ifZ=0              | 1(2)  | 1,2,3 |

| GOTO   | k    | Go to address             | $W.AND.k \rightarrow W$          | 2     |       |

| CALL   | k    | Call subroutine           | W.AND.f→d                        | 2     |       |

| RETURN | -    | Return from Subroutine    | $W.OR.k \rightarrow W$           | 2     |       |

| RETLW  | k    | Return with constant in W | W.OR.f→d                         | 2     |       |

| RETFIE | -    | Return from interrupt     | $W.XOR.k \rightarrow W$          | 2     |       |

#### **Directing a program flow**

#### Look-up tables Design:

- This instruction 'RETLW k' enables us to design easily the Look-up tables (lists).

- We use them by determining data position on our table adding it to the address at which the table begins, and then we read data from that location (which is usually found in program memory).

•Table can be formed as a subprogram which consists of a series of 'RETLW k' instructions, where 'k' constants are members of the table.

•We write the position of a member of our table in W register, and using CALL instruction to call a subprogram which creates the table.

• The instruction ADDWF PCL, f adds the position of a W register member to the starting address of our table, found in PCL register, and so we get the real data address in program memory.

•When returning from a subprogram we will have in W register the contents of an addressed table member.

Main molov 2 call Lookup Lookup addwf PCL, f retlw k retlw k1 : : : retlw k2

| N | NOP    | - | No Operation         |                |        | 1 |  |

|---|--------|---|----------------------|----------------|--------|---|--|

|   | CLRWDT | - | Clear Watchdog Timer | 0→WDT,→TO,1→PD | TO, PD | 1 |  |

| S | SLEEP  | - | Go into standby mode | 0→WDT,HTO,0→PD | TO, PD | 1 |  |

#### Other instructions

## **Instruction Execution Period**

All instructions are executed in one cycle except for conditional branch instructions if condition was true, or if the contents of program counter was changed by some instruction. In that case, execution requires two instruction cycles, and the second cycle is executed as NOP (No Operation). Four oscillator clocks make up one instruction cycle. If we are using an oscillator with 4MHz frequency, the normal time for executing an instruction is 1 µs, and in case of conditional branching, execution period is 2 µs.

| Syntax:<br>Description:<br>Operation:<br>Operand:<br>Flag:<br>Number of words:<br>Number of cycles: |                                    | •                   | 1                                                                              |

|-----------------------------------------------------------------------------------------------------|------------------------------------|---------------------|--------------------------------------------------------------------------------|

| Example 1 MOVLY                                                                                     | N O×5A                             |                     | OPTION_REG=0×20<br>W=0×40<br>OPTION_REG=0×40<br>W=0×40                         |

| After instruction:                                                                                  | W=O×5A                             | Example 2 MOVW      |                                                                                |

| Example 2 MOVLY                                                                                     | N REGISTAR                         | Before instruction: | W=0×17<br>FSR=0×C2                                                             |

|                                                                                                     | W=0×10 and REGISTAR=0×40<br>W=0×40 | After instruction:  | address contents 0×C2=0×00<br>W=0×17<br>FSR=0×C2<br>address contents 0×C2=0×17 |

| Syntax:<br>Description:                        | [ <i>label</i> ] MOVF <b>f</b> , <b>d</b><br>Contents of <b>f</b> register is stored in location determined by <b>d</b> operand.<br>If <b>d=0</b> , destination is <b>W</b> register.<br>If <b>d=1</b> , destination is <b>f</b> register itself.<br>Option <b>d=1</b> is used for testing the contents of <b>f</b> register because<br>execution of this instruction affects Z flag in STATUS register. |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:<br>Operand:                         | $ \begin{aligned} \mathbf{f} &\Rightarrow (\mathbf{d}) \\ 0 &\leq \mathbf{f} \leq 127 \\ \mathbf{d} \in [0, 1] \end{aligned} $                                                                                                                                                                                                                                                                           |

| Flag:<br>Number of words:<br>Number of cycles: | Z<br>1                                                                                                                                                                                                                                                                                                                                                                                                   |

| Example 1 MOVF                                 | FSR, O                                                                                                                                                                                                                                                                                                                                                                                                   |

| Before instruction:                            | FSR=0×C2<br>W=0×00                                                                                                                                                                                                                                                                                                                                                                                       |

| After instruction:                             | W=0×C2<br>Z=0                                                                                                                                                                                                                                                                                                                                                                                            |

| Example 2 MOVF                                 | INDF, O                                                                                                                                                                                                                                                                                                                                                                                                  |

| Before instruction:                            | W=0×17<br>FSR=0×C2<br>address contents 0×C2=0×00                                                                                                                                                                                                                                                                                                                                                         |

| After instruction:                             | W=0×17<br>FSR=0×C2<br>address contents 0×C2=0×00<br>Z=1                                                                                                                                                                                                                                                                                                                                                  |

| Syntax:<br>Description:               | [ <i>label</i> ] MOVF <b>f</b> , <b>d</b><br>Contents of <b>f</b> register is stored in location determined by <b>d</b> operand.<br>If <b>d=0</b> , destination is <b>W</b> register.<br>If <b>d=1</b> , destination is <b>f</b> register itself.<br>Option <b>d=1</b> is used for testing the contents of <b>f</b> register because<br>execution of this instruction affects Z flag in STATUS register. |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:<br>Operand:<br>Flag:       | $ \begin{aligned} \mathbf{f} &\Rightarrow (\mathbf{d}) \\ 0 &\leq \mathbf{f} \leq 127 \\ \mathbf{d} &\in [0,1] \\ Z \end{aligned} $                                                                                                                                                                                                                                                                      |

| Number of words:<br>Number of cycles: | 1                                                                                                                                                                                                                                                                                                                                                                                                        |

| Example 1 MOVF                        | FSR, O                                                                                                                                                                                                                                                                                                                                                                                                   |

| Before instruction:                   | FSR=0×C2<br>W=0×00                                                                                                                                                                                                                                                                                                                                                                                       |

| After instruction:                    | W=0×C2<br>Z=0                                                                                                                                                                                                                                                                                                                                                                                            |

| Example 2 MOVF                        | INDF, O                                                                                                                                                                                                                                                                                                                                                                                                  |

| Before instruction:                   | W=0×17<br>FSR=0×C2<br>address contents 0×C2=0×00                                                                                                                                                                                                                                                                                                                                                         |

| After instruction:                    | W=0×17<br>FSR=0×C2<br>address contents 0×C2=0×00<br>Z=1                                                                                                                                                                                                                                                                                                                                                  |

| Syntax:<br>Description:                                                  | [ <i>label</i> ] CLRW<br>Contents of <b>W</b> reqister evens out to zero,<br>and Z flag in STATUS register is set to one. | Syntax:<br>Description:                   | [ <i>label</i> ] CRLF <b>f</b><br>Contents of ' <b>f</b> ' register evens out to zero,<br>and Z flag in status register is set to one. |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Operation:<br>Operand:<br>Flag:<br>Number of words:<br>Number of cycles: | 1                                                                                                                         | •                                         |                                                                                                                                        |

| Example CLRW                                                             |                                                                                                                           | Example 1 CRLF                            | STATUS                                                                                                                                 |

| Before instruction:<br>After instruction:                                | W=0×55<br>W=0×00<br>Z=1<br>Z=1                                                                                            | Before instruction:<br>After instruction: |                                                                                                                                        |

| Example 2 CLRF                                                           | INDF                                                                                                                      | Example 2 CLRF                            | INDF                                                                                                                                   |

| Before instruction:<br>After instruction:                                | FSR=0×C2<br>address contents 0×C2=0×33<br>FSR=0×C2<br>address contents 0×C2=0×00<br>Z=1                                   | Before instruction:<br>After instruction: | FSR=0×C2<br>address contents 0×C2=0×33<br>FSR=0×C2<br>address contents 0×C2=0×00<br>Z=1                                                |

| Syntax:<br>Description:                                                  | [ <i>label</i> ] SWAPF <b>f</b> , <b>d</b><br>Upper and lower half of <b>f</b> register exchange places.<br>If <b>d=0</b> , result is stored in <b>W</b> register.<br>If <b>d=1</b> , result is stored in <b>f</b> register. |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:<br>Operand:<br>Flag:<br>Number of words:<br>Number of cycles: |                                                                                                                                                                                                                              |

| Example 1 SWAP                                                           | REG, O                                                                                                                                                                                                                       |

| Before instruction:<br>After instruction:                                | REG=0×F3<br>REG=0×F3<br>W=0×3F                                                                                                                                                                                               |

| Example 2 SWAP                                                           | REG, 1                                                                                                                                                                                                                       |

| Before instruction:<br>After instruction:                                |                                                                                                                                                                                                                              |

| Syntax:<br>Description: | [ <i>label</i> ] ADDLW <b>k</b><br>Contents of <b>W</b> register is added to 8-bit<br>constant <b>k</b> and result is stored in <b>W</b> register. | Syntax:<br>Description: | [ <i>label</i> ] ADDWF <b>f</b> , <b>d</b><br>Add contents of register <b>W</b> to register <b>f</b> .<br>If <b>d=0</b> , result is stored in <b>W</b> register.<br>If <b>d=1</b> , result is stored in <b>f</b> register. |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:              | $(W) + k \Rightarrow W$                                                                                                                            | Operation:              | $(W) + (f) \Rightarrow d$                                                                                                                                                                                                  |

| Operand:                | 0 ≤ <b>k</b> ≤ 255                                                                                                                                 | Operand:                | d ∈ [0,1]<br>0 ≤ f ≤ 127                                                                                                                                                                                                   |

|                         | C, DC, Z                                                                                                                                           | •                       | C, DC, Z                                                                                                                                                                                                                   |

| Number of words:        | • •                                                                                                                                                | Number of words:        |                                                                                                                                                                                                                            |

|                         |                                                                                                                                                    | Number of cycles:       | 1                                                                                                                                                                                                                          |

| Number of cycles        | . 1                                                                                                                                                |                         |                                                                                                                                                                                                                            |

|                         |                                                                                                                                                    | Example 1 ADDW          | F FSR, O                                                                                                                                                                                                                   |

| Example 1 ADDL          | W O×15                                                                                                                                             | Before instruction:     |                                                                                                                                                                                                                            |

| Defere instruction.     | M-0×10                                                                                                                                             | After instruction:      | FSR=0×C2                                                                                                                                                                                                                   |

| Before instruction:     |                                                                                                                                                    | After instruction:      | FSR=0×C2                                                                                                                                                                                                                   |

| After instruction:      | W=0×25                                                                                                                                             |                         | 138-6462                                                                                                                                                                                                                   |

|                         |                                                                                                                                                    | Example 2 ADDLV         | V INDF, 1                                                                                                                                                                                                                  |

| Example 2 ADDL          | W REG                                                                                                                                              | Before instruction:     | W=0×17                                                                                                                                                                                                                     |

|                         |                                                                                                                                                    | before instruction:     | FSR=0×C0                                                                                                                                                                                                                   |

| Before instruction:     | W=0×10                                                                                                                                             |                         | address contents 0×C2=0×20                                                                                                                                                                                                 |

|                         | register contents REG=0×37                                                                                                                         | After instruction:      | W=0×17                                                                                                                                                                                                                     |

| d fter instruction.     | •                                                                                                                                                  |                         | FSR=0×C2                                                                                                                                                                                                                   |

| After instruction:      | W=0×47                                                                                                                                             |                         | address contents 0×C2=0×37                                                                                                                                                                                                 |

| Syntax:<br>Description:<br>Operation:                      | [ <i>label</i> ] SUBLW <b>k</b><br>Contents of <b>W</b> register is s<br><b>k</b> constant, and result is st<br><b>k</b> - ( <b>W</b> ) ⇒ <b>W</b> |            | Syntax:<br>Description:                   | [ <i>label</i> ] SUBWF <b>f</b> , <b>d</b><br>Contents of <b>W</b> register is sub<br>the contents of <b>f</b> register.                         | tracted from |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Operand:<br>Flag:<br>Number of words:<br>Number of cycles: | 0 ≤ k ≤ 255<br>C, DC, Z<br>1                                                                                                                       |            | Operation:<br>Operand:                    | If $d=0$ , result is stored in W<br>If $d=1$ , result is stored in f result is stored in f result $(f) - (W) \Rightarrow d$<br>$0 \le f \le 127$ | -            |

| Example 1 SUBLY                                            | ₩ 0×03                                                                                                                                             |            | Flag:                                     | <b>d</b> ∈ [0,1]<br>C, DC, Z                                                                                                                     |              |

| Before instruction:<br>After instruction:                  | W=0×01, C=×, Z=×<br>W=0×02, C=1, Z=0                                                                                                               | Result > 0 | Number of words:<br>Number of cycles:     |                                                                                                                                                  |              |

| Before instruction:<br>After instruction:                  | W=0×03, C=×, Z=×<br>W=0×00, C=1, Z=1                                                                                                               | Result = 0 | Example 1 SUBW                            | F REG,1                                                                                                                                          |              |

| Before instruction:<br>After instruction:                  | W=0×04, C=×, Z=×<br>W=0×FF, C=0, Z=0                                                                                                               | Result < 0 | Before instruction:<br>After instruction: | REG=3, W=2, C=X, Z=X<br>REG=1, W=2, C=1, Z=0                                                                                                     | Result > 0   |

| Example 2 SUBLY                                            | N REG                                                                                                                                              |            | Before instruction:<br>After instruction: | REG=2, W=2, C=×, Z=×<br>REG=0, W=2, C=1, Z=1                                                                                                     | Result = 0   |

| Before instruction:<br>After instruction:                  | W=0×10<br>contents REG=0×37<br>W=0×27<br>C=1                                                                                                       | Result > 0 | Before instruction:<br>After instuction:  | REG=1, W=2, C=X, Z=X<br>REG=0XFF, W=2, C=0, Z=0                                                                                                  | Result < 0   |

| Syntax:<br>Description:                                                  | contents of                        | LW <b>k</b><br>peration logic .<br><b>W</b> register an<br>pred in <b>W</b> regi | d constant <b>k</b> . | Syntax:<br>Description: | [ <i>label</i> ] ANDWF <b>f</b> , <b>d</b><br>Performs operation of logic AND over<br>the contents of <b>W</b> and <b>f</b> registers.<br>If <b>d=0</b> , result is stored in <b>W</b> register. |      |

|--------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------|-----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Operation:<br>Operand:<br>Flag:<br>Number of words:<br>Number of cycles: | (₩) .AND.<br>0 ≤ k ≤ 255<br>Z<br>1 | k⇒W                                                                              |                       | Operand:                | d ∈ [0,1]<br>Z<br>5: 1                                                                                                                                                                           |      |

| Example 1 ANDLV                                                          | V O×5F                             |                                                                                  |                       | Example 1 AND           |                                                                                                                                                                                                  |      |

| Before instruction:<br>After instruction:                                |                                    | ; 0101 1111<br>; 1010 0011<br>; 0000 0011                                        | (O×A3)<br>            |                         | W=0×17, FSR=0×C2 ; 0001 0111 (0)<br>W=0×17, FSR=02 ; 1100 0010 (0)                                                                                                                               |      |

| Euromalo 9 - MDU                                                         |                                    | , 0000 0011                                                                      | (0×03)                |                         | ; 0000 0010 (0)                                                                                                                                                                                  | ×02) |

| Example 2 ANDLV                                                          | Y KEG                              |                                                                                  |                       | Example 2 AND           | WF FSR, O                                                                                                                                                                                        |      |

| Before instruction:                                                      | REG=0×37                           | ; 1010 0011<br>; 0011 0111                                                       | (O×A3)<br>(O×37)      | -                       | W=0×17, FSR=0×C2 ; 0001 0111 (0><br>W=0×02, FSR=0×C2 ; 1100 0010 (0>                                                                                                                             |      |

| After instruction:                                                       | W=UX23                             | ; 0010 0011                                                                      | (0×23)                |                         | ; 0000 0010 (0>                                                                                                                                                                                  | ×02) |

| Syntax:<br>Description:                   | [ <i>label</i> ] IORLW <b>k</b><br>Operation logic OR is performed<br>over the contents of <b>W</b> register<br>and over 8-bit constant <b>k</b> , and<br>result is stored in <b>W</b> register. | Syntax:[/abe/] IORWF f, dDescription:Operation logic OR is performed over<br>the contents of W and f registers.<br>If d=0, result is stored in W register.<br>If d=1, result is stored in f register. |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | ( <b>W</b> ) .OR. ( <b>k</b> ) ⇒ <b>W</b><br>0 ≤ <b>k</b> ≤ 255<br>Z<br>1                                                                                                                        | Operation:(W) .OR. (f) $\Rightarrow$ dOperand: $0 \le f \le 127$<br>d $\in [0,1]$ Flag:ZNumber of words:1Number of cycles:1                                                                           |

| Example 1 IORLV                           |                                                                                                                                                                                                  | Example 1 IORWF REG, 0                                                                                                                                                                                |

| Before instruction:<br>After instruction: |                                                                                                                                                                                                  | Before instruction: REG=0×13, W=0×91<br>After instruction: REG=0×13, W=0×93<br>Z=0                                                                                                                    |

| Example 2 IORLW                           | / REG                                                                                                                                                                                            | Example 2 IORWF REG, 1                                                                                                                                                                                |

| Before instruction:<br>After instruction: | W=0×9A<br>contenst REG=0×37<br>W=0×9F<br>Z=0                                                                                                                                                     | Before instruction: REG=0×13, W=0×91<br>After instruction: REG=0×93, W=0×91<br>Z=0                                                                                                                    |

| Syntax:<br>Description:                                                  | [ <i>label</i> ] XORLW <b>k</b><br>Operation exclusive OR (XOR) is<br>done over the contents of <b>W</b><br>register and constant <b>k</b> , and<br>result is stored in <b>W</b> register. |                            | Syntax:<br>Description: | [ <i>label</i> ] XORWF <b>f</b> , <b>d</b><br>Operation exclusive OR is performed over<br>the contents of <b>W</b> and <b>f</b> registers.<br>If <b>d=0</b> , result is stored in <b>W</b> register.<br>If <b>d=1</b> , result is stored in <b>f</b> register. |                                                                            |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Operation:<br>Operand:<br>Flag:<br>Number of words:<br>Number of cycles: |                                                                                                                                                                                            |                            |                         |                                                                                                                                                                                                                                                                |                                                                            |

| Example 1 XORLV                                                          | V O×AF                                                                                                                                                                                     |                            |                         | Example 1 XORV                                                                                                                                                                                                                                                 | VF REG, 1                                                                  |

| Before instruction:<br>After instruction:                                |                                                                                                                                                                                            | ; 1010 1111<br>; 1011 0101 | · · ·                   |                                                                                                                                                                                                                                                                | REG=0×AF, W=0×B5 ; 1010 1111 (0×AF)<br>REG=0×1A, W=0×B5 ; 1011 0101 (0×B5) |

|                                                                          |                                                                                                                                                                                            | ; 0001 1010                | (0×1A)                  |                                                                                                                                                                                                                                                                | ; 0001 1010 (0×1A)                                                         |

| Example 2 XORLW REG                                                      |                                                                                                                                                                                            |                            | Example 2 XORV          | VF REG,O                                                                                                                                                                                                                                                       |                                                                            |

| Before instruction:<br>After instruction:                                |                                                                                                                                                                                            | ; 1010 1111<br>; 0011 0111 |                         |                                                                                                                                                                                                                                                                | REG=0×AF, W=0×B5 ; 1010 1111 (0×AF)<br>REG=0×AF, W=0×1A ; 1011 0101 (0×B5) |

|                                                                          | Z=0                                                                                                                                                                                        | ; 0001 1000                | (0×18)                  |                                                                                                                                                                                                                                                                | ; 0001 1010 (O×1A)                                                         |

| Syntax:<br>Description:                                                  | [ <i>label</i> ] INCF <b>f</b> , <b>d</b><br>Increments f register by one.<br>If <b>d=0</b> , result is stored in <b>W</b> reg<br>If <b>d=1</b> , result is stored in <b>f</b> reg | Syntax:<br>Description:                                                  | [ <i>label</i> ] DECF <b>f</b> , <b>d</b><br>Decrements f register by one.<br>If <b>d=0</b> , result is stored in <b>W</b> reg<br>If <b>d=1</b> , result is stored in <b>f</b> reg |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:<br>Operand:<br>Flag:<br>Number of words:<br>Number of cycles: |                                                                                                                                                                                    | Operation:<br>Operand:<br>Flag:<br>Number of words:<br>Number of cycles: |                                                                                                                                                                                    |

| Example 1 INCF                                                           | REG, 1                                                                                                                                                                             | Example 1 DECF                                                           | REG, 1                                                                                                                                                                             |

| Before instruction:<br>After instruction:                                | REG=0×FF<br>Z=0<br>REG=0×00<br>Z=1                                                                                                                                                 | Before instruction:<br>After instruction:                                | Z=0                                                                                                                                                                                |

| Example 2 INCF                                                           | REG, O                                                                                                                                                                             | Example 2 DECF                                                           | REG, O                                                                                                                                                                             |

| Before instruction:<br>After instruction:                                | REG=0×10<br>W=×<br>Z=0<br>REG=0×10<br>W=0×11<br>Z=0                                                                                                                                | <b>`</b>                                                                 | REG=0×13<br>W=×<br>Z=0<br>REG=0×13<br>W=0×12<br>Z=0                                                                                                                                |

| Syntax:<br>Description:                                            | [ <i>label</i> ] COMF <b>f</b> , <b>d</b><br>Contents of <b>f</b> register is complemented<br>If <b>d=0</b> , result is stored in <b>W</b> register.<br>If <b>d=1</b> , result is stored in <b>f</b> register. |                                                                     | [ <i>label</i> ] BCF <b>f</b> , <b>b</b><br>Reset bit <b>b</b> in <b>f</b> register.<br>(0) ⇒ <b>f<b></b><br/>0 &lt; <b>f</b> &lt; 107</b> |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                    | $\overline{(\mathbf{f})} \Rightarrow \mathbf{d}$ $0 \le \mathbf{f} \le 127$ $\mathbf{d} \in [0,1]$ $Z$ $1$                                                                                                     |                                                                     | 1                                                                                                                                          |

|                                                                    | REG=0×13 ; 0001 0011 (0×13)<br>REG=0×13 ; complement<br>W=0×EC                                                                                                                                                 | Before instruction:<br>After instruction:<br><b>Example 2</b> BCF I | REG=0×C7; 1100 0111 (0×C7)<br>REG=0×47; 0100 0111 (0×47)<br>NDF, 3                                                                         |

| <b>Example 2</b> COMF<br>Before instruction:<br>After instruction: |                                                                                                                                                                                                                | Before instruction:<br>After instruction:                           | W=0×17<br>FSR=0×C2<br>address contents (FSR)=0×2F<br>W=0×17<br>FSR=0×C2<br>address contents (FSR)=0×27                                     |

| Syntax:                                                                                                                                                                                | [ <i>label</i> ] BSF f, b                            | Syntax:                                                                          | [ <i>label</i> ] BTFSC <b>f</b> , <b>b</b> |                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------|

| Description:                                                                                                                                                                           | Set bit <b>b</b> in <b>f</b> register.               | Description:                                                                     | -                                          | equals zero, then we skip the next instruction.                                              |

|                                                                                                                                                                                        | 1 ⇒ f <b></b>                                        |                                                                                  |                                            | during execution of the current instruction,                                                 |

| Operand:                                                                                                                                                                               | 0 ≤ f ≤ 127                                          |                                                                                  |                                            | xt one is disabled, and NOP instruction executes<br>the current one a two-cycle instruction. |

|                                                                                                                                                                                        | 0 ≤ <b>b</b> ≤ 7                                     | Operation:                                                                       | -                                          | · · · · · · · · · · · · · · · · · · ·                                                        |

| Flag:                                                                                                                                                                                  | -                                                    | Operand:                                                                         |                                            |                                                                                              |

| Number of words:                                                                                                                                                                       |                                                      |                                                                                  | $0 \le \mathbf{b} \le 7$                   |                                                                                              |

| Number of cycles:                                                                                                                                                                      | 1                                                    | Flag:                                                                            | -                                          |                                                                                              |

| Example 1 BSF F                                                                                                                                                                        | REG, 7                                               | Number of v<br>Number of c                                                       | vords: 1<br>:ycles: 1 or 2 depen           | ding on a <b>b</b> bit                                                                       |

|                                                                                                                                                                                        | REG=0×07;00000111 (0×07)<br>REG=0×17;10000111 (0×17) | Example                                                                          |                                            |                                                                                              |

|                                                                                                                                                                                        |                                                      | LAB_01                                                                           | BTFSC REG,1                                | ;Test bit no.1 in REG                                                                        |

| Example 2 BCF I                                                                                                                                                                        | INDF, 3                                              | LAB_02<br>LAB_03                                                                 |                                            | ;Skip this line if =0<br>;Skip here if =1                                                    |

| Before instruction:                                                                                                                                                                    | W=0×17<br>FSR=0×C2                                   | Before instruc                                                                   | ction, program count                       | er was at address LAB_01.                                                                    |

| address contents (FSR)=0×20       After instruction, if the first bit in REG register was zero,         After instruction:       W=0×17         address concents       address LAB_03. |                                                      | REG register was zero, program counter points to                                 |                                            |                                                                                              |

|                                                                                                                                                                                        | FSR=0×C2<br>address contents (FSR)=0×28              | If the first bit in REG register was one, program counter points to address LAB_ |                                            |                                                                                              |

| Syntax:         | [ <i>label</i> ] BTFSS <b>f</b> , <b>b</b> |                                                  |     | Syntax:      | [ <i>label</i> ] INCFSZ <b>f</b> , <b>d</b>            |

|-----------------|--------------------------------------------|--------------------------------------------------|-----|--------------|--------------------------------------------------------|

| Description     | :If bit <b>b</b> in <b>f</b> register (    | equals one, then skip over the next instruction  |     | Description  | : Contents of f register is incremented by or          |

|                 | If bit <b>b</b> equals one, o              | during execution of the current instruction, the |     | · ·          | If d=0, result is stored in W register.                |

|                 | next one is disabled,                      | and NOP instruction is executed instead, thus    |     |              | If <b>d=1</b> , result is stored in <b>f</b> register. |

|                 |                                            | one a two-cycle instruction.                     |     |              | If result =0, the next instruction is execute          |

| Operation:      | Skip next instruction                      | if (f <b>)=1</b>                                 |     |              | the current one a two-cycle instruction.               |

| Operand:        | 0 ≤ <b>f</b> ≤ 127                         | · · ·                                            |     | Operation:   | $(f) + 1 \Rightarrow d$                                |

| · ·             | 0 ≤ <b>b</b> ≤ 7                           |                                                  |     | Operand:     | 0 ≤ <b>f</b> ≤ 127                                     |

| Flaq:           | -                                          |                                                  |     | · ·          | <b>d</b> ∈ [0,1]                                       |

| Number of       | words: 1                                   |                                                  |     | Flag:        | -                                                      |

| Number of       | cycles: 1 or 2 deper                       | iding on a <b>b</b> bit                          |     | Number of    | words: 1                                               |

|                 |                                            |                                                  |     | Number of    | cycles: 1 or 2 depending on a result                   |

| Example         |                                            |                                                  |     |              |                                                        |

|                 |                                            |                                                  |     | Example      |                                                        |

| LAB_01          | BTFSS REG,1                                | ;Test bit no.1 in REG                            |     |              |                                                        |

| LAB_02          |                                            | ;Skip this line if =1                            |     | LAB_01       | INCESZ REG, 1 ; Increase the contents                  |

| LAB_03          |                                            | ;Skip here if =0                                 |     | LAB_02       | ; Skip this line if =0                                 |

|                 |                                            |                                                  |     | LAB_03       | ; Skip here if =0                                      |

| Before instru   | iction, program count                      | er was at address LAB_01                         |     |              |                                                        |

|                 |                                            |                                                  |     | The contents | s of program counter before instruction, PC=           |

| After instruc   | tion, if the first bit in I                | REG register was one, program counter points     | to  |              |                                                        |

| address LAB     |                                            | 5                                                |     | The contents | s of REG after executing an instruction REG=           |

|                 | _                                          |                                                  |     | program cou  | nter points to label address LAB_03. Otherw            |

| If the first bi | it in REG register was                     | zero, program counter points to address LAB_     | 02. | points to ad | dress of the next instruction or to LAB_02.            |

|                 | ~                                          |                                                  |     |              |                                                        |

d ister is incremented by one. stored in **W** register. stored in **f** register. next instruction is executed as NOP making two-cycle instruction. pending on a result ; Increase the contents REG by one. ; Skip this line if =0 ; Skip here if =0 ter before instruction, PC=address LAB\_01 uting an instruction REG=REG+1, if REG=0, l address LAB\_03. Otherwise, pc

| Syntax:<br>Description:                                                                                                                 | [ <i>label</i> ] DECFSZ <b>f</b> , <b>d</b><br>Contents of <b>f</b> register is decr by one.<br>If <b>d=0</b> , result is stored in <b>W</b> register.<br>If <b>d=1</b> , result is stored in <b>f</b> register.<br>If result = 0, next instruction is<br>executed as NOP, thus making the<br>current one, a two-cycle instruction. | Syntax:[/abe/] GOTO kDescription:Unconditional jump to address k.Operation: $k \Rightarrow PC < 10:0>$ , (PCLATH <4:3>) $\Rightarrow PC < 12:11>$ Operand: $0 \le k \le 2048$ |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:                                                                                                                              | $(f) - 1 \Rightarrow d$                                                                                                                                                                                                                                                                                                             | Flag: _                                                                                                                                                                       |

| Operand:                                                                                                                                | 0 ≤ f ≤ 127<br>d = [0,1]                                                                                                                                                                                                                                                                                                            | Number of words: 1                                                                                                                                                            |

| Flaq:                                                                                                                                   | d ∈ [0,1]<br>-                                                                                                                                                                                                                                                                                                                      | Number of cycles: 2                                                                                                                                                           |

| Number of word                                                                                                                          | ls: 1<br>es: 1 or 2 depending on a result                                                                                                                                                                                                                                                                                           | Example                                                                                                                                                                       |

| Example                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                     | LAB_00 GOTO LAB_01 ; Jump to LAB_01                                                                                                                                           |

| LAB_02                                                                                                                                  | Z CNT, 1 ; Decr the contents REG by one<br>; Skip this line if = 0<br>; Skip here if = 1                                                                                                                                                                                                                                            | e<br>LAB_01                                                                                                                                                                   |

| The contents of program counter before instruction,<br>PC=address LAB_01<br>The contents of CNT register after executing an instruction |                                                                                                                                                                                                                                                                                                                                     | Before instruction: PC=address LAB_00<br>After instruction: PC=address LAB_01                                                                                                 |

| CNT=CNT-1, if CNT=0,                                                                                                                    |                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                               |

| Otherwise, prog                                                                                                                         | points to address of label LAB_03.<br>ram counter points to<br>lowing instruction, or to LAB_02.                                                                                                                                                                                                                                    |                                                                                                                                                                               |

| Syntax:<br>Description                                   | [ <i>label</i> ] CALL <b>k</b><br>: Instruction calls a subprogram. First, return<br>address (PC+1) is stored on stack, then 11-bit<br>direct operand <b>k</b> , which contains the subprogram<br>address, is stored in program counter. | Syntax:<br>Description:                                           | [ <i>label</i> ] RETURN<br>Contents from the top of a stack |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|

| Operation:                                               | (PC) + 1 ⇒ Top Of Stack (TOS)<br>$\mathbf{k}$ ⇒ PC<10:0>, (PCLATH<4:3>) ⇒ PC<12:11>                                                                                                                                                      |                                                                   | is stored in program counter.                               |

| Operand:<br>Flag:<br>Number of<br>Number of (<br>Example |                                                                                                                                                                                                                                          | Operation:<br>Operand:<br>Flag:<br>Number of wor<br>Number of cyc |                                                             |

| · ·                                                      | CALL LAB_02 ; Call subrutine LAB_02<br>;                                                                                                                                                                                                 | <b>Example</b> RE                                                 | ETURN                                                       |

| LAB_02                                                   | :<br>                                                                                                                                                                                                                                    | Before instructio                                                 | on: PC=×<br>TOS=×                                           |

| Before instru<br>After instruc                           | ction: PC=address LAB_01<br>TOS=×<br>tion: PC=address LAB_02<br>TOS=LAB_01                                                                                                                                                               | After instruction                                                 |                                                             |

| Description:<br>Operation:<br>Operand:<br>Flag:<br>Number of w<br>Number of c | -<br>Iords: 1                                      | Syntax:[label] RETFIEDescription:Return from a subbroaram. Value<br>from TOS is stored in PC. Interrupts<br>are enabled by setting a GIE bit.Operation:TOS ⇒ PC; 1 ⇒ GIEOperand:-Flag:-Number of words:1Number of cycles:2 |

|-------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Before instruc                                                                |                                                    | Example RETFIE                                                                                                                                                                                                             |

| After instructi                                                               | PC=X<br>TOS=X<br>on: W=0X43<br>PC=TOS<br>TOS=TOS-1 | Before instruction: PC=X<br>GIE=0<br>After instruction: PC=TOS                                                                                                                                                             |