# CMCS 611-101 Advanced Computer Architecture

#### Lecture 9

### **Pipeline Implementation Challenges**

#### October 5, 2009

www.csee.umbc.edu/~younis/CMSC611/CMSC611.htm

## Lecture's Overview

#### **Previous Lecture:**

#### ➔ Control hazards

Limiting the effect of control hazards via branch prediction and delay

Static branch prediction techniques and performance

Branch delay issues and performance

#### ➔ Exceptions handling

- •Categorizing of exception based on types and handling requirements

- •Issues of stopping and restarting instructions in a pipeline

- •Precise exception handling and the conditions that enable it

- •Instructions set effects on complicating pipeline design

#### ❑ <u>This Lecture</u>

- ➔ Pipelining floating point operations

- ➔ An example pipeline: MIPS R4000

# **Floating-Point Pipeline**

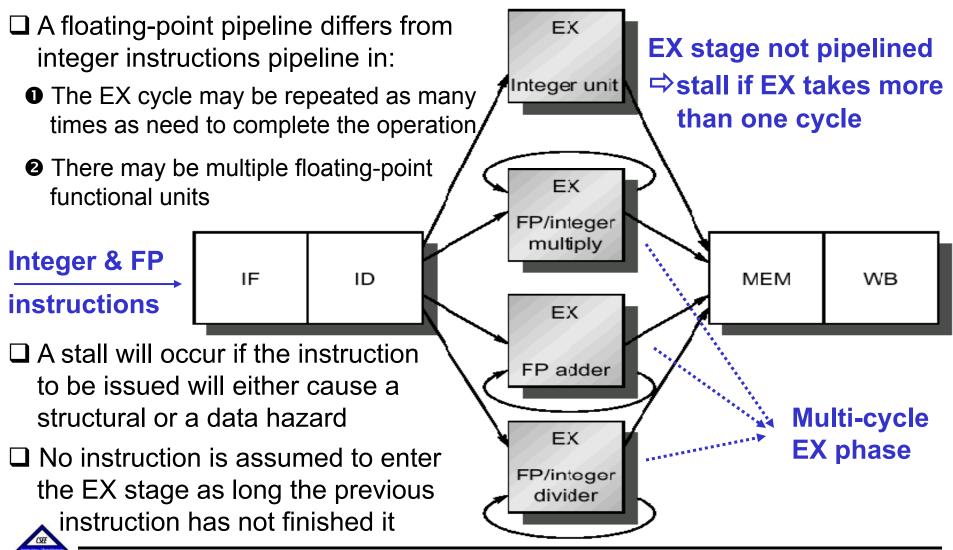

□ It is impractical to require that all MIPS floating point operations complete in one clock cycle (complex logic and/or very long clock cycle)

# **Multi-cycle FP Pipeline**

| MULTD | IF | ID | M1 | M2 | M3 | M4  | M5        | M6  | M7 | MEM | WB |

|-------|----|----|----|----|----|-----|-----------|-----|----|-----|----|

| ADDD  |    | IF | ID | A1 | A2 | A3  | <b>A4</b> | MEM | WB |     |    |

| LD    |    |    | IF | ID | EX | MEM | WB        |     |    |     |    |

| SD    |    |    |    | IF | ID | EX  | MEM       | WB  |    |     |    |

Example: blue indicate where data is needed and red when result is available

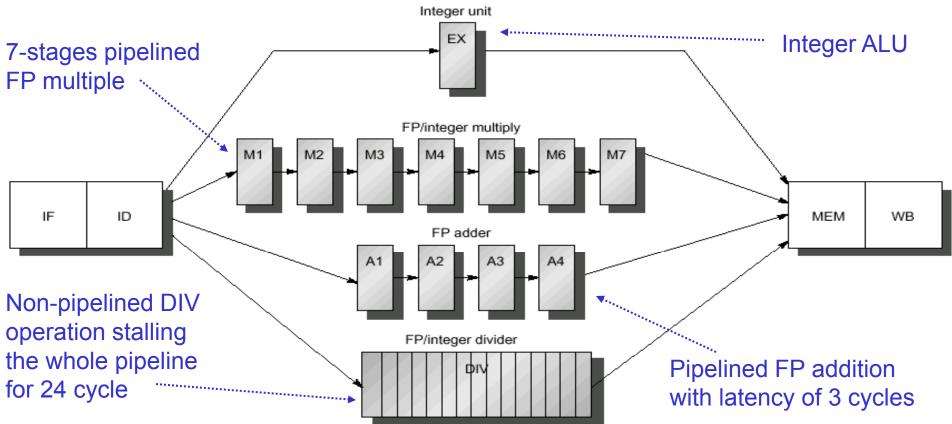

# Multi-cycle FP Pipeline EX Phase

- Example: assume that floating point add, subtract and multiply can be performed in stages while integer and FP divide cannot

- Latency: the number of intervening cycles between an instruction that produces a result and an instruction that uses it

- □ Since most operations consume their operands at the beginning of the EX stage, latency is usually the number of stages in the EX an instruction uses

- □ Naturally long latency increases the frequency of RAW hazards

- Initiation (Repeat) interval: the number of cycles that must elapse between issuing two operations of a given type

| Functional unit                     | Latency | Initiation interval |

|-------------------------------------|---------|---------------------|

| Integer ALU                         | 0       | 1                   |

| Data memory (integer and FP loads)  | 1       | 1                   |

| FP add                              | 3       | 1                   |

| FP multiply (also integer multiply) | 6       | 1                   |

| FP divide (also integer divide)     | 24      | 25                  |

Example of typical latency of floating point operations

# **FP Pipeline Challenges**

#### Issues:

- > Because the divide unit is not fully pipelined, structural hazards can occur

- Because the instructions have varying running times, the number of register writes required in a cycle can be larger than 1

- > WAW hazards are possible, since instructions no longer reach WB in order

- WAR hazards are NOT possible, since register reads are still taking place during the ID stage

- Instructions can complete in a different order than they were issued, causing problems with exceptions

- Longer latency of operations makes stalls for RAW hazards more frequent

| Instruction      |    | Clock cycle number |    |       |    |       |       |       |       |       |       |     |    |       |       |       |     |

|------------------|----|--------------------|----|-------|----|-------|-------|-------|-------|-------|-------|-----|----|-------|-------|-------|-----|

|                  | 1  | 2                  | 3  | 4     | 5  | 6     | 7     | 8     | 9     | 10    | 11    | 12  | 13 | 14    | 15    | 16    | 17  |

| LD F4, 0(R2)     | IF | ID                 | ΕX | MEM   | WB |       |       |       |       |       |       |     |    |       |       |       |     |

| MULTD F0, F4, F6 |    | IF                 | ID | stall | M1 | M2    | M3    | M4    | M5    | M6    | M7    | MEM | WB |       |       |       |     |

| ADDD F2, F0, F8  |    |                    | IF | stall | ID | stall | stall | stall | stall | stall | stall | A1  | A2 | A3    | A4    | MEM   |     |

| SD 0(R2), F2     |    |                    |    |       | IF | stall | stall | stall | stall | stall | stall | ID  | EX | stall | stall | stall | MEM |

Example of RAW hazard caused by the long latency

## Write-Caused Structural Hazard

| Instruction      | Clock cycle number |    |    |    |     |     |    |     |     |     |    |  |

|------------------|--------------------|----|----|----|-----|-----|----|-----|-----|-----|----|--|

|                  | 1                  | 2  | 3  | 4  | 5   | 6   | 7  | 8   | 9   | 10  | 11 |  |

| MULTD F0, F4, F6 | IF                 | ID | M1 | M2 | M3  | M4  | M5 | M6  | M7  | MEM | WB |  |

|                  |                    | IF | ID | EX | MEM | WB  |    |     |     |     |    |  |

|                  |                    |    | IF | ID | EX  | MEM | WB |     |     |     |    |  |

| ADDD F2, F4, F6  |                    |    |    | IF | ID  | A1  | A2 | A3  | A4  | MEM | WB |  |

|                  |                    |    |    |    | IF  | ID  | EX | MEM | WB  |     |    |  |

|                  |                    |    |    |    |     | IF  | ID | EX  | MEM | WB  |    |  |

| LD F2, 0(R2)     |                    |    |    |    |     |     | IF | ID  | EX  | MEM | WB |  |

- At cycle 11, the MULTD, ADDD and LD instructions will try to write back causing structural hazard if there is only one write port

- Additional write ports are not cost effective since they are rarely used and it is better to detect and resolve the structural hazard

- Structural hazards can be detected at the ID stage and the instruction will be stalled to avoid a conflict with another at the WB

- □ Alternatively, structural hazards can be handled at the MEM or WB by rescheduling the usage of the write port

#### WAW Data Hazards

| Instruction      | Clock cycle number |    |    |    |     |     |    |     |     |     |    |  |

|------------------|--------------------|----|----|----|-----|-----|----|-----|-----|-----|----|--|

|                  | 1                  | 2  | 3  | 4  | 5   | 6   | 7  | 8   | 9   | 10  | 11 |  |

| MULTD F0, F4, F6 | IF                 | ID | M1 | M2 | M3  | M4  | M5 | M6  | M7  | MEM | WB |  |

|                  |                    | IF | ID | EX | MEM | WB  |    |     |     |     |    |  |

|                  |                    |    | IF | ID | EX  | MEM | WB |     |     |     |    |  |

| ADDD F2, F4, F6  |                    |    |    | IF | ID  | A1  | A2 | A3  | A4  | MEM | WB |  |

|                  |                    |    |    |    | IF  | ID  | EX | MEM | WB  |     |    |  |

| LD F2, 0(R2)     |                    |    |    |    |     | IF  | ID | EX  | MEM | WB  |    |  |

|                  |                    |    |    |    |     |     | IF | ID  | EX  | MEM | WB |  |

□ WAW hazards can be corrected by either:

- Stopping the latter instruction (LD in example) at the MEM until it is safe

- Preventing the first instruction from overwriting the register

- Correcting WAW Hazards at cycle 11 is not problematic unless there is an instruction between ADDD and LD that read F2 causing RAW hazard

- □ WAW hazards can be detected at the ID stage and thus the first instruction can be converted to no-op

- □ Since WAW hazards are generally very rare, designers usually go with the

## **Detecting Hazards**

- Hazards can occur among FP instructions and among FP and integer instructions

- Using separate register files for integer and FP limits potential hazards to just FP load and store instructions

- Assuming all checks are to be performed in the ID phase, hazards can be detected through the following steps:

- Check for structural hazards:

- Wait if the functional unit is busy (Divides in our case)

- Make sure the register write port is available when needed

- Check for a RAW data hazard

- Requires knowledge of latency and initiation interval to decide when to forward and when to stall

- Check for a WAW data hazard

- Write completion has to be estimated at the ID stage to check with other instructions in the pipeline

Data hazard detection and forwarding logic can be derived from values stored at the data stationary between the different stages

# **Maintaining Precise Exception**

- Pipelining FP instructions can cause out-of-order completion since FP operations are different in length

- □ Although data hazard solutions prevent the effect of out-of-order instruction completion on the semantics, exception handling can be problematic

Example: DIVD F0, F2, F4

ADDD F10, F10, F8

SUBD F12, F12, F14

ADDD and SUBD will complete before DIVD completes without causing any data hazards

What if an exception occurs while DIVD executes in a point of time after ADDD overwrites F10 !!

□ There are four possible approaches to deal with FP exception handling:

- Settle for imprecise exceptions (restrict # active FP instructions)

- IEEE floating point standard requires precise exceptions

- Some supercomputers still uses this approach

- Some machines offer slow precise and fast imprecise exceptions

- **2** Buffer the results of all operations until previous instructions complete

- Complex and expensive design (many comparators and large MUX)

- History or future register file are practical implementations that allow

- for restoring original machine state in case of exception

# **Precise Exception Approaches (Cont.)**

□ Four possible approaches to deal with FP exception handling (cont.):

• Allow imprecise exceptions and get the handler to clean up any miss

- Simply save PC and some state about the interrupting instruction and all out-of-order completed instructions

- The trap handler will consider the state modification caused by finished instructions and prepare machine to resume correctly

- Issues: consider the following example

Instruction<sub>1</sub>: A long-running instr. that eventually get interrupted

Instructions 2 ... (n-1): A series of instructions that are not complete

Instruction n: An instruction that is finished

- → The trap handler will have a complex job to deal with

- The compiler can simplify the problem by grouping FP instructions so that the trap does not have to worry about unrelated instructions

- Allow instruction issue to continue only if previous instruction are guaranteed to cause no exceptions:

- Mainly applied in the execution phase

- Used on MIPS R4000 and Intel Pentium

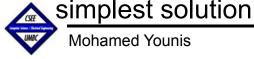

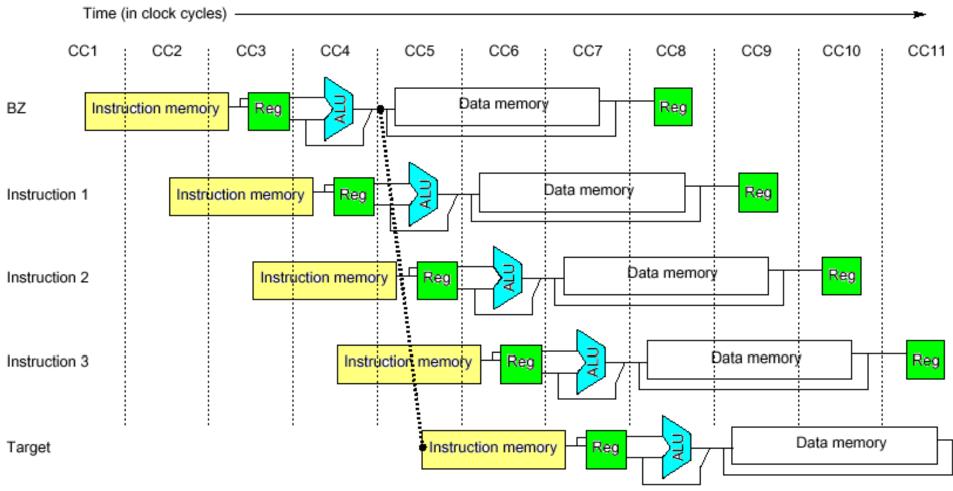

## **Performance of FP Pipeline**

Average number of stalls per instruction mainly affected by latency and number of cycles before results are used but not by instruction frequency (except for divide)

- Stalls are mainly caused by:

- Latency of the divide instruction

SPEC Benchmark

Ë

- RAW hazards

- WAW hazards are possible but rare in practice

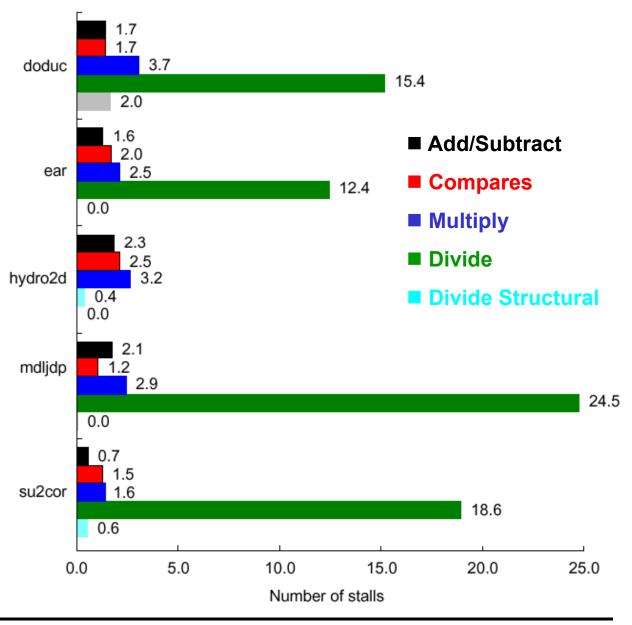

## **Performance of FP Pipeline (Cont.)**

The total number of stalls/instr. range from 0.65 to 1.21 with average 0.87

FP result stalls dominate in all cases with average of 0.71 (82% of all stalls)

Compares generate an average of 0.1 stalls and are second largest source

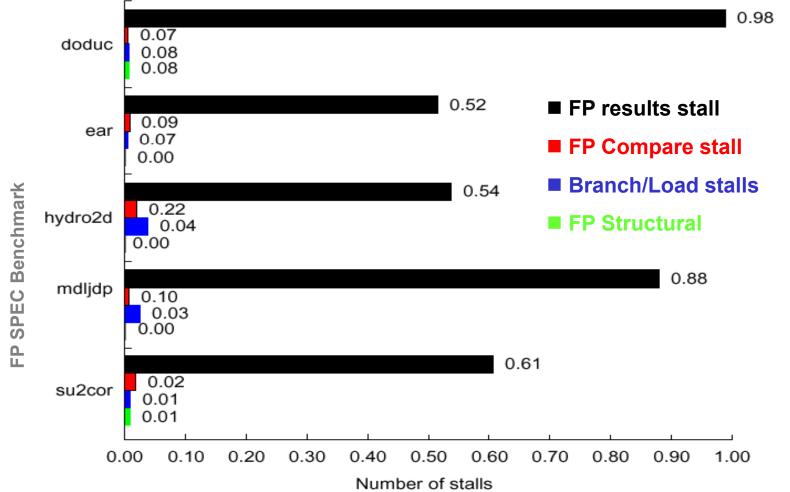

# **MIPS 4000 Pipeline**

□ Implements the MIPS-3 64-bit instruction

Uses 8 stages pipeline through pipelining instruction and data cache access

Deeper pipeline allows for higher clock rate but increases load/branch delays

**IF:** First half of instr. fetch; PC selection, initiation of instruction cache access

**IS:** Second half of the instruction fetch completing instruction cache access

**RF:** Instr. Decode, register fetch, hazard checking and instr. cache hit detection

**EX:** ALU operations, effective address calculation, and condition evaluation

- **DF**: Data fetch, first half of data cache access

- **DS**: Second half of data fetch, completion of data cache access

- **TC:** Tag check, determine whether the data cache access hit

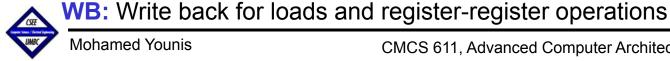

## **Load Delays**

- Data value are available at the end of the DS cycle, cause a two cycle delay for load instructions

- Pipelined cache access increases the need for forwarding and complicates the forwarding logic

A cache miss will stall the pipeline additional one (or more) cycles

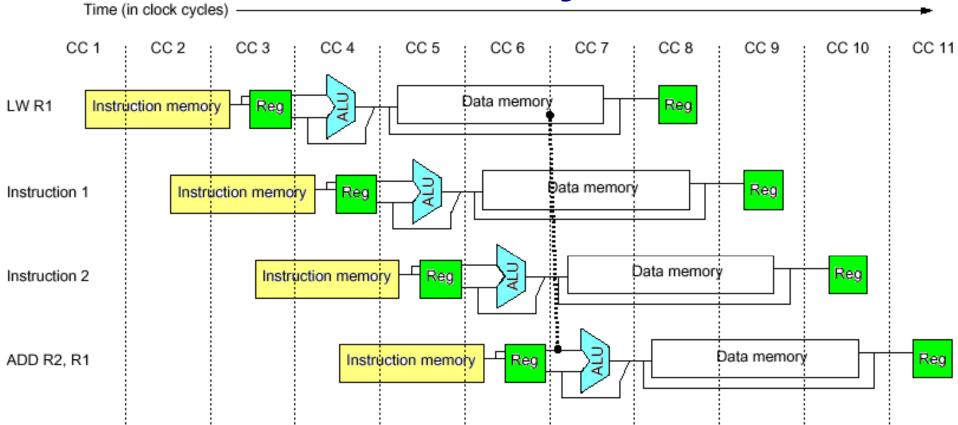

# **Branching Delays**

Branch conditions are computed during EX stage extending the basic branch delay to 3 cycles

MIPS allows for a single-cycle delay branching and a predict-not-taken strategy for the remaining two branching delay cycles

# MIPS 4000 FP Pipeline

□ Three FP functional units: adder, multiplier and divider, with the adder logic serving as the final step of the a multiply and divide

| Stage | Functional Unit | Description                |

|-------|-----------------|----------------------------|

| Α     | FP adder        | Mantissa ADD stage         |

| D     | FP Divider      | Divide pipeline stage      |

| E     | FP Multiplier   | Exception test stage       |

| Μ     | FP Multiplier   | First stage of multiplier  |

| Ν     | FP Multiplier   | Second stage of multiplier |

| R     | FP adder        | Rounding stage             |

| S     | FP adder        | Operand shift stage        |

| U     |                 | Unpack FP numbers          |

□ The FP functional unit can be thought as having eight different stages, combined in different order to execute various FP operations

An instruction can use a stage zero or multiple times and in different orders

| <b>FP</b> Instruction | Latency   | Pipeline stages                                     |

|-----------------------|-----------|-----------------------------------------------------|

| Add/Subtract          | 4         | U, S+A, A+R, R+S                                    |

| Multiply              | 8         | U, E+M, M, M, M, N, N+A, R                          |

| Divide                | 36        | U, A, R, D <sup>27</sup> , D+A, D+R, D+A, D+R, A, R |

| Compare               | 3         | U, A, R                                             |

| Mohamed Younis        | CMCS 611, | Advanced Computer Architecture                      |

## **Performance of MIPS Pipeline**

# Conclusion

#### □ <u>Summary</u>

- ➔ Exceptions handling

- Categorizing of exception based on types and handling requirements

- Issues of stopping and restarting instructions in a pipeline

- Precise exception handling and the conditions that enable it

- Instructions set effects on complicating pipeline design

- ➔ Pipelining floating point instruction

- Multi-cycle operation of the pipeline execution phase

- Hazard detection and resolution

- Exception handling and FP pipeline performance

- → An example pipeline: MIPS R4000

#### □ <u>Next Lecture</u>

- ➔ Instruction level parallelism

- ➔ Dynamic instruction scheduling

Reading assignment includes sections A.5 & A.6, in the textbook