### Philadelphia University

### Student Name: Student Number: Serial Number:

### Final Exam, First Semester: 2018/2019 Dept. of Computer Engineering

|                      | 1 1                 | 8 8           | -          |

|----------------------|---------------------|---------------|------------|

| <b>Course Title:</b> | Logic Circuits      | Date:         | 03/01/2019 |

| <b>Course No:</b>    | 630211              | Time Allowed: | 2 hours    |

| Lecturer:            | Dr. Qadri Hamarsheh | No. Of Pages: | 7          |

Instructions:

- ALLOWED: pens and drawing tools (no red color).

- NOT ALLOWED: Papers, calculators, literatures and any handouts. Otherwise, it will lead to the non-approval of your examination.

• Shut down Telephones, and other communication devices.

Please note:

- This exam paper contains 6 questions totaling 40 marks

- Write your name and your matriculation number on every page of the solution sheets.

- All solutions together with solution methods (explanatory statement) must be inserted in the labelled position on the solution sheets.

- You can submit your exam after the first hour.

**Basic notions:** The aims of the questions in this part are to evaluate the required minimal student knowledge and skills. Answers in the pass category represent the minimum understanding of basic concepts: Digital Systems, Binary Number Systems, Boolean Algebra, Basic Logic Gates, Boolean Expression Simplification, Karnaugh Maps, and Combinational Sequential Circuits.

### <u>Question 1</u> Multiple Choice

Identify the choice that best completes the statement or answers the question.

(10 marks)

1) Which of the following is **not a weighted** value positional numbering system:

|    | a)                                  | hexadecimal                         | b)         | binar <del>y</del> |

|----|-------------------------------------|-------------------------------------|------------|--------------------|

|    | c)                                  | binary-coded decimal                | d)         | octal              |

| 2) | Convert <b>527<sub>8</sub></b> to b | pinary.                             |            |                    |

| -  | a)                                  | 011100111                           | b)         | 101010111          |

|    | c)                                  | 111010101                           | d)         | 343                |

| 3) | The Gray code                       | of the binary number <b>0101</b> is |            |                    |

|    | a)                                  | 1111                                | <b>b</b> ) | 1000               |

|    | c) (                                | 0111                                | d)         | None of the above  |

| 4) | Simplification of                   | the Boolean expression $AB$ +       | ABC +      | ABCD + ABCDE +     |

- 4) Simplification of the Boolean expression AB + ABC + ABCD + ABCDE + ABCDEF yields which of the following results?

- a) AB b) AB + CD + EF

- c) ABCDEF d) A + B + C + D + E + F

**5)** Applying **DeMorgan's Law** to  $f = \overline{AB} + \overline{C}(E + \overline{D})$  will result in:

a)  $f = \overline{A} + \overline{B} + \overline{C} + \overline{E} + D$ b)  $f = \overline{A} \ \overline{B} \ \overline{C} + E \overline{D}$ c)  $f = \overline{A} \ \overline{B} \ \overline{C} + (E + \overline{D})$ d)  $f = \overline{A} + \overline{B} + \overline{C} + \overline{E}D$  6) From the truth table below, determine the standard **SOP** expression.

|            | Inputs                                                            |   | Output |  |  |

|------------|-------------------------------------------------------------------|---|--------|--|--|

| A          | В                                                                 | C | X      |  |  |

| 0          | 0                                                                 | 0 | 0      |  |  |

| 0          | 0                                                                 | 1 | 1      |  |  |

| 0          | 1                                                                 | 0 | 0      |  |  |

| 0          | 1                                                                 | 1 | 1      |  |  |

| 1          | 0                                                                 | 0 | 0      |  |  |

| 1          | 0                                                                 | 1 | 0      |  |  |

| 1          | 1                                                                 | 0 | 1      |  |  |

| 1          | 1                                                                 | 1 | 0      |  |  |

| a)         | a) X=ĀĒC+ĀBC+ABĒ                                                  |   |        |  |  |

| b)         | $X = \overline{A}\overline{B}\overline{C} + ABC + A\overline{B}C$ |   |        |  |  |

| <i>c)</i>  | X=ABC+ABC+ABC                                                     |   |        |  |  |

| <b>d</b> ) | X=ABC+ABC+ABC                                                     |   |        |  |  |

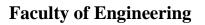

7) The logic function implemented by the circuit below is (ground implies a logic "0")

8) The characteristic equation of **S-R** latch is

Q(n+1) = S'R + Q(n)Ra) Q(n+1) = SR + Q(n)RC)

Q(n+1) = (S + Q(n))R'b) d) Q(n+1) = S'R + Q'(n)R

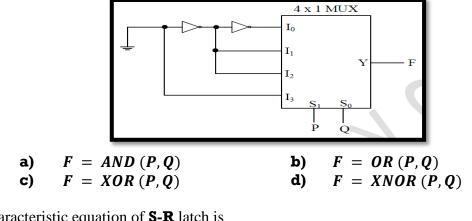

9) The figure shown below is ------

- a) A T flip flop C)

- A JK flip flop

- **An S-R latch**

- d) A D flip flop

- **10)**A ripple counter is a(n) ------ device

- asynchronous a)

- C) synchronous

- Combinational b)

- d) None of them

### **Question 2**

(6 marks)

a) Prove the identity of the following Boolean equation, using algebraic manipulation: (2 marks)

# $\overline{A}B + \overline{B}\overline{C} + AB + \overline{B}C = 1$

| Solution |

|----------|

|          |

|          |

|          |

|          |

|          |

|          |

b) Draw 4-bit asynchronous binary counter using JK flip flops and its timing diagram. (4 marks)

## Solution

**Familiar and Unfamiliar Problems Solving:** The aim of the questions in this part is to evaluate that the student has some basic knowledge of the key aspects of the lecture material and can attempt to solve familiar and unfamiliar problems of Combinational and Sequential Circuits and Analysis of Sequential Circuits.

| Question 3 | Implement full adder circuit using 4:1 multiplexers. | (4 marks) |

|------------|------------------------------------------------------|-----------|

|            | Solution                                             |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

|            |                                                      |           |

5

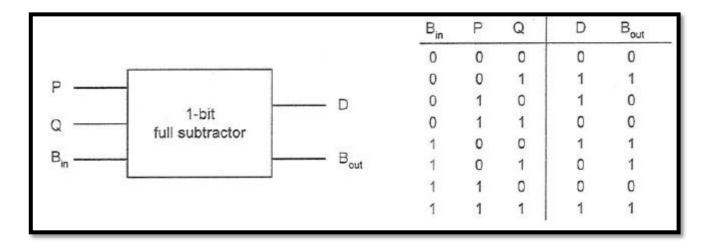

Question 4

Where **P** and **Q** are 1-bit variables and  $B_{in}$  is borrow input from the previous stage. It produces two outputs: the difference **D** and the borrow output  $B_{out}$ . The truth table describing the function of this 1-bit full subtractor is shown in table.

$P-Q-B_{in}$

Do the following:

- a) Derive the Boolean expressions for **D** and *B<sub>out</sub>* using **K-map**.

- b) Implement **D** and  $B_{out}$  logic circuits.

- c) Design the 1-bit full subtractor using **3x8 decoder**.

### Solution

The **1-bit full subtractor** shown in the following figure performs the binary subtraction

(7 marks)

(3 marks) (2 marks) (2 marks)

### <u>Question 5</u>

(6 marks)

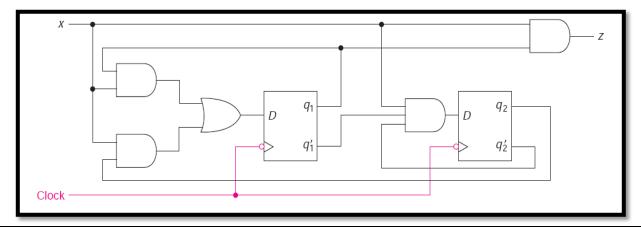

Derive the Next-state and Output equations, Next-state table, and draw the state diagram for the sequential circuit shown in the following figure. There is one input, x, and one output, z.

# Solution

(7 marks)

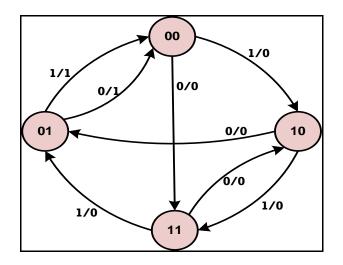

<u>Question 6</u> Given the following state diagram, design a clocked sequential circuit using JK flip-flops.

# GOOD LUCK