Philadelphia University Faculty of Engineering

# **Marking Scheme**

Examination Paper Department of CE

## Module: Microprocessors (630313)

Final Exam

First Semester

Date: 21/01/2019

Section 1

Weighting 40% of the module total

Lecturer:

Coordinator:

Internal Examiner:

Dr. Qadri Hamarsheh

Dr. Qadri Hamarsheh

Dr. Naser Halasa

### Marking Scheme Microprocessors (630313)

The presented exam questions are organized to overcome course material, the exam contains 7 questions; *all questions* are compulsory requested to be answered. Thus, the student is permitted to answer any question out of the existing ones in this section.

#### Marking Assignments

The following scheme shows the marks assignments for each question. They show also the steps for which a student can get marks along the related procedure he/she achieves.

**Question 1** This question is attributed with 10 marks if answered properly The answer for this question as the following:

The answer for this question as the following:

a) (I) and (II) and (III)

c) (II) and (III) only

The first processor that includes real mode in the Intel microprocessor family was ----- a) 8085

b) 8086

| a) 0005                                                    | D) 8080                                                 |

|------------------------------------------------------------|---------------------------------------------------------|

| c) <mark>80286</mark>                                      | d) 80386                                                |

| 2) Which of the following is an <b>invalid</b> ins         |                                                         |

| a) add dx,dx                                               | b) MOV AX, CS                                           |

| c) sub bar,5                                               | d) MOV AL, DI                                           |

| 3) The <b>directive</b> that can be used to de             | declare variables to store binary-coded decimal numbers |

| (packed BCD Integers) is                                   |                                                         |

| a) SWORD                                                   | b) REAL10                                               |

| c) QWORD                                                   | d) TBYTE                                                |

| 4) The variable definition smallArray by                   | yte 2Ch, 5 DUP ("exam") will reserve bytes of           |

| memory.                                                    |                                                         |

| a) 21                                                      | b) 26                                                   |

| c) 6                                                       | d) None of above                                        |

| 5) The output of the linker (LINK command                  | ,                                                       |

| a) .lis                                                    | b) .obj                                                 |

| c) .lnk                                                    | d) .exe                                                 |

| · •                                                        | d Zero flags after the following instructions have      |

| executed?                                                  |                                                         |

| mov ax,620h                                                |                                                         |

| sub ah,0F6h                                                |                                                         |

| a) S=0,Z=1                                                 | b) S=0,Z=0                                              |

| c) S=1,Z=0                                                 | d) $S=1,Z=1$                                            |

| <b>7)</b> The conditional branch instruction <b>JNS</b> pe |                                                         |

| a) ZF =0                                                   | b) <b>PF=0</b>                                          |

| c) <b>SF=0</b>                                             | d) CF=0                                                 |

| 8) The instruction <b>TEST</b> is most similar to          |                                                         |

| a) OR                                                      | b) AND                                                  |

| c) XOR                                                     | d) NOT                                                  |

| 9) The interrupt vector for <b>INT 17H</b> is store        |                                                         |

| a) 0005CH                                                  | b) 00068H                                               |

| c) 000C5H                                                  | d) 00017H                                               |

|                                                            |                                                         |

| <b>10)</b> Which of the following are performed wh         |                                                         |

| (I) FLAGS register is pushe                                |                                                         |

| (II) CS register is pushed to                              |                                                         |

| (III) IP register is pushed to                             | to the stack                                            |

|                                                            |                                                         |

b) (I) and (II) only

d) (I) and (III) only

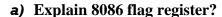

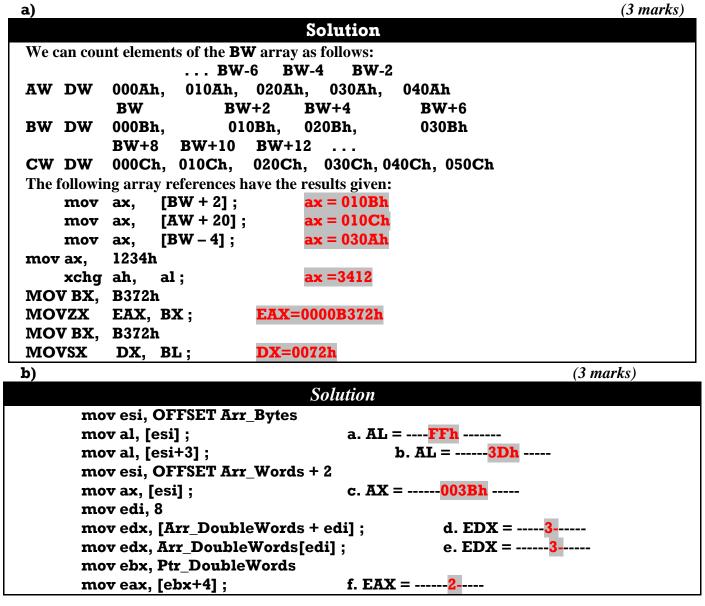

Question 2 This question is attributed with 6 marks if answered properly

(3 marks)

#### Solution Carry Flag (CF) - this flag is set to 1 when there is an unsigned overflow. For 1. example when you add bytes 255 + 1 (result is not in range 0...255). When there is no overflow this flag is set to 0. Parity Flag (PF) - this flag is set to 1 when there is even number of one bits in 2. result, and to 0 when there is odd number of one bits. Auxiliary Flag (AF) - set to 1 when there is an unsigned overflow for low nibble 3. (4 bits). Zero Flag (ZF) - set to 1 when result is zero. For non-zero result this flag is set 4. to 0. Sign Flag (SF) - set to 1 when result is negative. When result is positive it is set 5. to 0. (This flag takes the value of the most significant bit.) Trap Flag (TF) - Used for on-chip debugging. 6. Interrupt enable Flag (IF) - when this flag is set to 1 CPU reacts to interrupts 7 from external devices. 8. Direction Flag (DF) - this flag is used by some instructions to process data chains, when this flag is set to 0 - the processing is done forward, when this flag is set to 1 the processing is done backward. **Overflow Flag (OF)** - set to 1 when there is a signed overflow. For example, 9. when you add bytes 100 + 50 (result is not in range -128...127). b) What is the use of Interrupt vector table of 8086 microprocessor? (2 marks Solution The interrupt vector table contains 256 four byte entries, containing the CS:IP interrupt vectors for each of the 256 possible interrupts. The table is used to locate the interrupt service routine addresses for each of those interrupts. **IVT Format** 0000:0000 Offset 0000:0001 Interrupt 0 IP LSB 0000:0002 Segment IP MSB 0000:0003 CS LSB 0000:0004 Offset 0000:0005 CS MSB Interrupt 1 0000:0006 Segment 0000:0007 Given a Vector, where is the ISR address stored in memory ? • $Offset = Type \times 4$ 0000:03fc Offset Example: int 36h 0000:03fd Interrupt 255 0000:03fe Offset = (54×4) = 216 Segment 0000:03££ = 00d8h c) What is an instruction queue? Explain? (1 mark) Solution

This is introduced in 8086 processor. This queue is in the BIU and is used for storing the predecoded instructions. This will overlap the fetching and execution cycle. The EU will take the instructions from the queue for decoding and execution.

**Question 3** This question is attributed with 4 marks, if answered properly. The answer for this question as the following:

| Write instruction(s) to perform the following tasks: |  |

|------------------------------------------------------|--|

|                                                      |  |

| 1) | Multiply AX by 5                                                                         | MOV CX, 5<br>MUL CX                              |

|----|------------------------------------------------------------------------------------------|--------------------------------------------------|

| 2) | Three different instructions that will clear the contents of register CL                 | 1) MOV CL, 0H<br>2) XOR CL, CL<br>3) SUB, CL, CL |

| 3) | Jump to label 'HELP' if AX is<br>negative                                                | TEST AX, 8000H<br>JNZ HELP                       |

| 4) | sets (1) the right most five bits of DI<br>without changing the remaining<br>bits of DI. | OR DI,001FH                                      |

**Question 4** This question is attributed with 6 marks, if answered properly.

The complete code for this question as the following:

**Question 5** This question is attributed with 5 marks, if answered properly. The answer for this question as the following:

| The answer for this question as the following | Solution  |

|-----------------------------------------------|-----------|

| Title string operation                        |           |

| .model small                                  |           |

| .stack 100h                                   |           |

| .data                                         |           |

| String db "exercise",0                        |           |

| Length db (\$-String) -1                      |           |

| Ans db ?                                      | (1 mark)  |

| .code                                         |           |

| Main proc                                     |           |

| MOV AX, @data                                 |           |

| MOV DS, AX                                    |           |

| MOV AL,00H                                    |           |

| MOV SI, offset String                         |           |

| MOV CX, Length                                | (1 mark)  |

| Back: MOV BH, [SI]                            |           |

| CMP BH, 'e'                                   |           |

| JNZ Label                                     |           |

| INC AL                                        |           |

| Label: INC SI                                 |           |

| LOOP Back                                     |           |

| MOV Ans, AL                                   |           |

| MOV AH, 4CH                                   |           |

| INT 21H                                       |           |

| Main endp                                     |           |

| End Main                                      | (3 marks) |

**Question 6** This question is attributed with 3 marks, if answered properly. The answer for this question as the following:

|                       | Solution |

|-----------------------|----------|

| mov ax, A             |          |

| cmp ax, B             |          |

| jne DoIF              |          |

| mov ax, X             |          |

| cmp ax, Y             |          |

| jng EndOfIf           |          |

| mov ax, Z             |          |

| cmp ax, T             |          |

| jnl EndOfIf           |          |

| ; THEN Block:         |          |

| DoIf: mov ax, D       |          |

| mov C, ax             |          |

| ; End of IF statement |          |

| EndOfIF:              |          |

**Question 7** This question is attributed with 6 marks, if answered properly. The answer for t his question as the following:

| Title ArraysOperations<br>.model small<br>.data<br>InputArr db 1,2,3,1,3,5,6,3,4,5<br>OddÄrr db 10 dup(?)<br>EvenÄrd db 0<br>EvenÄdd db 0<br>.code<br>Main PROC<br>mov ax,@data<br>mov ds,ax<br>LEA BX,InputArr<br>LEA SI,OddÄrr<br>LEA SI,OddÄrr<br>LEA SI,OddÄrr<br>LEA SI,OddÄrr<br>LEA SI,OddÄrr<br>LEA DI,EvenÄrr<br>mov cx,10<br>mov dh,02<br>(2 marks)<br>L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00<br>(1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddÄdd,dl<br>INC BX<br>Loop L1<br>jmp CAL<br>Loop L1<br>INC BX<br>Loop L1<br>INC BX<br>Loop L1<br>(1 mark)<br>CAL:<br>mov ax,0000<br>mov al,OddÄdd<br>mov ax,0000<br>mov al,OddÄdd<br>mov ax,0000<br>mov al,OddÄdd<br>mov ax,0000 | So                              | lution    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------|

| .model small<br>data<br>InputArr db 1,2,3,1,3,5,6,3,4,5<br>OddArr db 10 dup(?)<br>EvenArr db 10 dup(?)<br>OddAd db 0<br>EvenArd db 0<br>.code<br>Main PROC<br>mov ax,@data<br>mov ds,ax<br>LEA BX,InputArr<br>LEA BX,InputArr<br>LEA DI,EvenArr<br>mov cx,10<br>mov dh,02 (2 marks)<br>L1:<br>mov ah,00<br>mov al,18X]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov ax,4C00h                                                                                                                                   |                                 |           |

| InputArr db 1,2,3,1,3,5,6,3,4,5<br>OddArr db 10 dup(?)<br>EvenArd b10 dup(?)<br>OddAdd db 0<br>EvenAdd db 0<br>.code<br>Main PROC<br>mov ax,@data<br>mov ds,ax<br>LEA BX,InputArr<br>LEA SI,OddArr<br>LEA DI,EvenArr<br>mov cx,10<br>mov dh,02<br>L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00<br>(1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL<br>Loop L1<br>(1 mark)<br>EVVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1<br>(1 mark)<br>CAL:<br>mov ax,0000<br>mov ax,4C00h                                                                                                                                         |                                 |           |

| OddArr db 10 dup(?)     EvenArr db 10 dup(?)     OddAdd db 0     EvenAdd db 0     .code     Main PROC     mov ax,@data     mov ds,ax     LEA BX,InputArr     LEA SI,OddArr     LEA SI,OddArr     LEA DLEvenArr     mov cx,10     mov dh,02   (2 marks)     L1:     mov al,[BX]     mov dl,al     div dh     cmp ah,00   (1 mark)     je EVEN1     mov [D1],d1     add OddAdd,d1     INC BX     Loop L1   (1 mark)     EVEN1:     mov [S1],d1     add EvenAdd,d1     INC SX     Loop L1   (1 mark)     EVEN1:     mov [S1],d1     add EvenAdd,d1     INC SX     Loop L1   (1 mark)     CAL:     mov ax,0000     mov bx,0000     mov bd,OddAdd     mov ax,4C00h                                                        | .data                           |           |

| EvenÄrr db 10 dup(?)<br>OddÄdd db 0<br>EvenÄdd db 0<br>.code<br>Main PROC<br>mov ax,@data<br>mov ds,ax<br>LEA BX,InputÄrr<br>LEA SI,OddÄrr<br>LEA DI,EvenÄrr<br>mov cx,10<br>mov dh,02 (2 marks)<br>L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddÄdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenÄdd,dl<br>INC SI<br>INC SX<br>Loop L1 (1 mark)<br>CÄL:<br>mov ax,0000<br>mov ax,4C00h                                                                                                                                                                                                            | InputArr db 1,2,3,1,3,5,6,3,4,5 |           |

| OddAdd db 0<br>EvenAdd db 0<br>.code<br>Main PROC<br>mov ax,@data<br>mov ds,ax<br>LEA BX,InputArr<br>LEA BX,InputArr<br>LEA DI,EvenArr<br>mov cx,10<br>mov dh,02 (2 marks)<br>L1:<br>mov ah,00<br>mor al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mor [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mor ax,0000<br>mor bx,0000<br>mor bx,0000<br>mor ad,OddAdd<br>mor x,4C00h                                                                                                                                                                                    | OddArr db 10 dup(?)             |           |

| EvenAdd db 0<br>.code<br>Main PROC<br>mov ax,@data<br>mov ds,ax<br>LEA BX,InputArr<br>LEA SI,OddArr<br>LEA DI,EvenArr<br>mov cx,10<br>mov dh,02 (2 marks)<br>L1:<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC SI<br>INC SX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bL,EvenAdd<br>mov al,OddAdd<br>mov ax,4C00h                                                                                                                                                                                                                   | EvenArr db 10 dup(?)            |           |

| .code<br>Main PROC<br>mov ax,@data<br>mov ds,ax<br>LEA BX,InputArr<br>LEA SI,OddArr<br>LEA DJ,EvenArr<br>mov cx,10<br>mov dh,02 (2 marks)<br>L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC SI<br>INC SX<br>Loop L1 (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC SX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bk,0000<br>mov bk,0000<br>mov bk,0000<br>mov bk,0000<br>mov ax,4C00h                                                                                                          | OddAdd db 0                     |           |

| Main PROC<br>mov ax,@data<br>mov ds,ax<br>LEA BX,InputArr<br>LEA BX,InputArr<br>LEA DI,EvenArr<br>mov cx,10<br>mov dh,02 (2 marks)<br>L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                  | EvenAdd db 0                    |           |

| mov ax,@data<br>mov ds,ax<br>LEA BX,InputArr<br>LEA SI,OddArr<br>LEA DI,EvenArr<br>mov cx,10<br>mov dh,02 (2 marks)<br>L1:<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],d1<br>add OddAdd,d1<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],d1<br>add EvenAdd,d1<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                    | .code                           |           |

| mov ds,ax<br>LEA BX,InputArr<br>LEA SI,OddArr<br>LEA DI,EvenArr<br>mov cx,10<br>mov dh,02 (2 marks)<br>L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov b,0000<br>mov b,0000<br>mov ax,4C00h                                                                                                                                                                                                                                                                        | Main PROC                       |           |

| LEA BX, InputArr<br>LEA SI, OddArr<br>LEA DI, EvenArr<br>mov cx, 10<br>mov dh, 02 (2 marks)<br>L1:<br>mov ah, 00<br>mov al, [BX]<br>mov dl, al<br>div dh<br>cmp ah, 00 (1 mark)<br>je EVEN1<br>mov [DI], dl<br>add OddAdd, dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI], dl<br>add EvenAdd, dl<br>INC SI<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax, 0000<br>mov b, 0000<br>mov ax, 4C00h                                                                                                                                                                                                                                                                              | mov ax,@data                    |           |

| LEA SI,OddArr<br>LEA DI,EvenArr<br>mov cx,10<br>mov dh,02<br>(2 marks)<br>L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00<br>(1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC SI<br>INC SI<br>INC SX<br>Loop L1<br>(1 mark)<br>EVEN1:<br>mov as,0000<br>mov ba,0000<br>mov bl,EvenAdd<br>mov as,4C00h                                                                                                                                                                                                                                                                                  | -                               |           |

| LEA DI, EvenArr<br>mov cx, 10<br>mov dh, 02 (2 marks)<br>L1:<br>mov ah, 00<br>mov al, [BX]<br>mov dl, al<br>div dh<br>cmp ah, 00 (1 mark)<br>je EVEN1<br>mov [DI], dl<br>add OddAdd, dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI], dl<br>add EvenAdd, dl<br>INC SX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                           |                                 |           |

| mov cx,10<br>mov dh,02 (2 marks)<br>L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                          | -                               |           |

| mov dh,02 (2 marks)<br>L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC SX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov b,0000<br>mov b,0000<br>mov a,4C00h                                                                                                                                                                                                                                                                                                                                                              | -                               |           |

| L1:<br>mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,000<br>mov bx,000<br>mov bx,000<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                     | -                               |           |

| mov ah,00<br>mov al,[BX]<br>mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                      | -                               | (2 marks) |

| mov al, [BX]<br>mov dl, al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI], dl<br>add OddAdd, dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI], dl<br>add EvenAdd, dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov bx,0000<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                 |                                 |           |

| mov dl,al<br>div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                     | -                               |           |

| div dh<br>cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],d1<br>add OddAdd,d1<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],d1<br>add EvenAdd,d1<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |           |

| cmp ah,00 (1 mark)<br>je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov al,Codh                                                                                                                                                                                                                                                                                                                                                                                                                            | -                               |           |

| je EVEN1<br>mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |           |

| mov [DI],dl<br>add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | (I mark)  |

| add OddAdd,dl<br>INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov bl,EvenAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                               |           |

| INC DI<br>INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],d1<br>add EvenAdd,d1<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |           |

| INC BX<br>Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],d1<br>add EvenAdd,d1<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov bx,0000<br>mov bl,EvenAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                               |           |

| Loop L1<br>jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],d1<br>add EvenAdd,d1<br>INC SI<br>INC SX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov al,OddAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |           |

| jmp CAL (1 mark)<br>EVEN1:<br>mov [SI],d1<br>add EvenAdd,d1<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |           |

| EVEN1:<br>mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —                               | (1 mark)  |

| mov [SI],dl<br>add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | · -                             | (I Mark)  |

| add EvenAdd,dl<br>INC SI<br>INC BX<br>Loop Ll (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                               |           |

| INC SI<br>INC BX<br>Loop L1 (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |           |

| INC BX<br>Loop Ll (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                               |           |

| Loop Ll (1 mark)<br>CAL:<br>mov ax,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |           |

| CAL:<br>mov ax,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | (1 mark)  |

| mov ax,0000<br>mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                               | ()        |

| mov bx,0000<br>mov al,OddAdd<br>mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | mov ax,0000                     |           |

| mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                               |           |

| mov bl,EvenAdd<br>mov ax,4C00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •                               |           |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                               |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | mov ax,4C00h                    |           |

| INT 61N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | int 21h                         |           |

| Main endp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Main endp                       |           |

| End Main (1 mark)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | End Main                        | (1 mark)  |